Product Summary

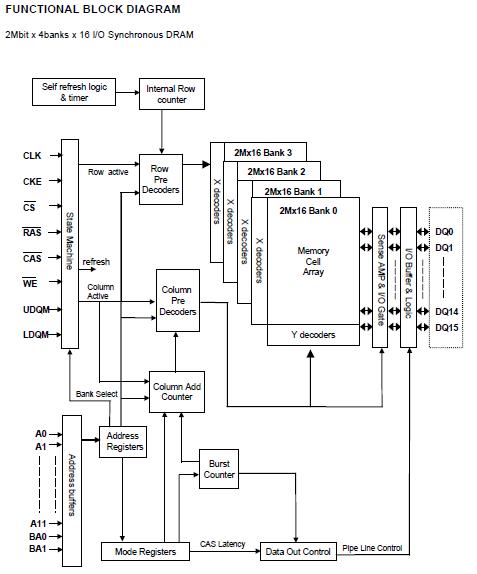

The Hynix HY5V26EFP-H is a 134,217,728bit CMOS Synchronous DRAM, ideally suited for the main memory applications which require large memory density and high bandwidth. HY5V26EFP-H is organized as 4banks of 2,097,152x16 HY5V26C(L/S)F is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths of HY5V26EFP-H are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.

Parametrics

HY5V26EFP-H absolute maximum ratings: (1)Ambient Temperature: 0 ~ 70 ℃; (2)Storage Temperature: -55 ~ 125 ℃; (3)Voltage on Any ball relative to VSS: -1.0 ~ 4.6 V; (4)Voltage on VDD relative to VSS: -1.0 ~ 4.6 V; (5)Short Circuit Output Current: 50 mA; (6)Power Dissipation: 1 W; (7)Soldering Temperature·Time: 260·10 ℃·Sec.

Features

HY5V26EFP-H features: (1)Single 3.3±0.3V power supply; (2)All device balls are compatible with LVTTL interface; (3)54Ball FBGA (10.5mm x 8.3mm); (4)All inputs and outputs referenced to positive edge of system clock; (5)Data mask function by UDQM or LDQM; (6)Internal four banks operation; (7)Auto refresh and self refresh; (8)4096 refresh cycles / 64ms.

Diagrams

|

HY5V22(L)F(P) |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5V22GF |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5V22LFP |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5V26CF |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5V52LF |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5V62CF |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))